Fujitsu Develops Virtual Router Acceleration Technology To Deliver Ultra-High-Speed Packet Processing Performance

Fujitsu Laboratories Ltd. today announced the development of technology to accelerate virtual routers, which play a major role in the functionality of networks in virtual environments.

Server virtualization, which concentrates multiple applications and the infrastructure functionality of network processing in a general-purpose server environment, is spreading beyond datacenters to the field of edge computing, including wireless base stations and Mobile Edge Computing (MEC)(1). The technology also proves useful in areas including societal infrastructure with applications like traffic management, and in entertainment, where it can be used to deliver viewers content like sporting events. As data volumes increase and systems become increasingly complex, however, the CPU resources required for packet processing in a virtual network increase. This reduces the number of applications that can run on a single server, and leads to lower server aggregation rates.

To resolve this issue, Fujitsu Laboratories has now developed technology to accelerate packet address control, which had been a performance bottleneck, while also offloading the processing of router functions in the virtual network to field programmable gate arrays (FPGAs)(2). This speeds up packet processing performance eighteen-fold compared with existing virtual routers, while reducing the use of CPU resources to about one thirteenth that of existing technology.

With this technology, Fujitsu Laboratories will deliver high performance virtual networks with a low computational burden, supporting the digital transformation of companies by improving server utilization efficiency for businesses that will use large volumes of data in the 5G era.

Development Background and Issues

Server virtualization, which concentrates multiple applications and network processing functionality using a virtual environment on a general-purpose server, is becoming increasingly common and widespread as digital transformation progresses. Moreover, by accelerating digital transformation within a wide variety of companies, new services are also being created that link applications together. Against this background, the volumes of data handled by these applications is trending upwards, leading to issues of increasing network complexity and increased computational burdens.

As networks grow increasingly complex and computational burdens increase, issues have arisen with improving packet processing performance in the virtual routers that are essential to flexible network structures, as well as with reducing the CPU resources used for network processing, in the effort to deliver efficient server virtualization. By resolving these issues, it will become possible to increase the number of applications that can run on a server, as well as decrease the number of servers needed for a system, reducing investment costs for customers.

About the Newly Developed Technology

Fujitsu Laboratories has now developed technology to offload the burden of virtual router functionality from the CPU to FPGAs, alongside technology to increase the speed of packet addressing control. This will not only increase network performance, but will also significantly reduce the CPU resources used for network processing.

1. High Speed Packet Addressing Control Technology

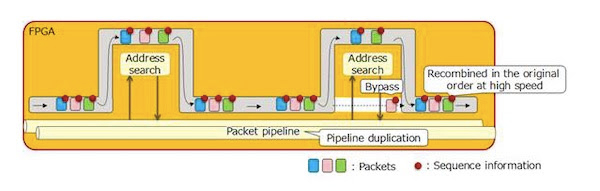

Previously, high-speed processing was conducted by subjecting all packets to the same processing, without changing the order of the packets. If the order of the packets were to change in the input or the output of the virtual router processing, that might lead to applications resending packets, which would lower quality and increase the burden on the system.

With this technology, packet sequence information is stored separately from the packets in the pipeline. Consequently, in address search processing spread over multiple stages, when the results of an earlier search render subsequent searches unnecessary and a packet bypasses those searches, it can be rapidly recombined with the other packets in the pipeline in the proper order based on the packet pipeline sequence information. Combined with the pipeline duplication, this technique reduces memory access while maintaining high pipeline processing speeds. These technologies improve packet processing performance.

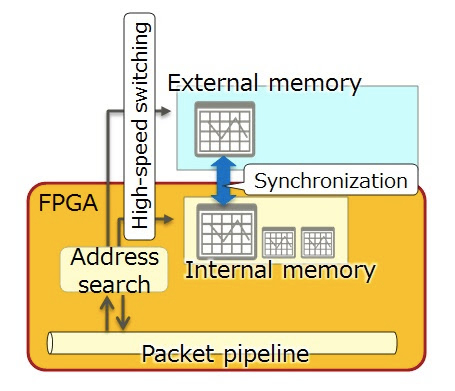

2. Hybrid Memory Management Technology of Lookup Tables

Fujitsu Laboratories has developed technology to automatically switch between the high-speed, low-capacity memory within the FPGAs and the high-capacity external memory, without pausing address search processing. In address search processing, multiple tables are searched to determine the address. As the number of connections increases, the amount of memory used by the lookup tables increases and the free space in the internal memory becomes insufficient. When this happens, this technology can synchronize lookup tables with relatively low access frequency, relative to their size, with external memory in the background, automatically switching to lookup tables in external memory without stopping search processing. This enables stable packet processing performance, limiting access to external memory, even in cases such as large-scale systems, where there are many communication destinations, and large lookup tables become essential.

Effects

An evaluation of the effects of this offloading on a general-purpose server was conducted using this technology, which was deployed on Intel Stratix 10 MX FPGA featuring high-speed HBM2(3) memory using Tungsten FabricTM, an exemplary open-source virtual router. Two servers connected with 100Gbps ethernet ran four virtual machines each, and communications were conducted between each virtual machine to test the performance of the virtual routers. The results showed that packet processing performance, which was 13.8Mpps using existing methods, was increased to 250Mpps, or about an 18-fold increase. In addition, the number of CPU cores used was reduced from 13 cores to 1 core.

Using this technology, it is now possible to increase application server density. This will support the digital transformation of customers from the foundational level, improving server utilization efficiency in infrastructure business areas that use large volumes of data in the 5G era, particularly in base stations and MEC for carrier businesses, such as, for example, making it possible to operate a video distribution service for a stadium with fewer servers.

Future Plans

Fujitsu Laboratories will continue to improve the performance and expand the functionality of this technology, as well as conducting further evaluations based on customer digital transformation use cases, with the goal of commercialization during fiscal 2021.

(1)

Mobile Edge Computing (MEC)

Technology primarily

used in mobile communications networks that delivers reduced

latency and a more distributed burden for core networks by

conducting data processing using servers and storage

distributed to locations such as base

stations.

(2) Field programmable gate arrays

(FPGAs)

Field programmable gate arrays are

large-scale semiconductor devices for which logic circuits

can be rewritten.

(3) HBM2

The

memory that is built into the same package as the FPGAs

which is capable of transfer data at high-speed and

high-capacity.

NIWA: Students Representing New Zealand At The ‘Olympics Of Science Fairs’ Forging Pathway For International Recognition

NIWA: Students Representing New Zealand At The ‘Olympics Of Science Fairs’ Forging Pathway For International Recognition Coalition to End Big Dairy: Activists Protest NZ National Dairy Industry Awards Again

Coalition to End Big Dairy: Activists Protest NZ National Dairy Industry Awards Again Infoblox: Dancing With Scammers - The Telegram Tango Investigation

Infoblox: Dancing With Scammers - The Telegram Tango Investigation Consumer NZ: This Mother’s Day, Give The Gift Of Scam Protection And Digital Confidence

Consumer NZ: This Mother’s Day, Give The Gift Of Scam Protection And Digital Confidence NZ Airports Association: Airlines And Airports Back Visa Simplification

NZ Airports Association: Airlines And Airports Back Visa Simplification Netsafe: Statement From Netsafe About Proposed Social Media Ban

Netsafe: Statement From Netsafe About Proposed Social Media Ban